- 下載位址: [www.ed2k.online][高性能仿真器].Fintronic.Super.FinSim.v7.0.18.ISO-TBE[www.xuexi111.com].bin

- 下載位址: [www.ed2k.online][高性能仿真器].Fintronic.Super.FinSim.v7.0.18.ISO-TBE[www.xuexi111.com].cue

- 下載位址: [www.ed2k.online][高性能仿真器].Fintronic.Super.FinSim.v7.0.18.ISO-TBE[www.xuexi111.com].nfo

資料介紹

未通過安全和安裝測試,使用後果自負與本論壇無關

軟件版權歸原作者及原軟件公司所有,如果你喜歡,請購買正版軟件

注:此鏈接下載轉自:TLF論壇

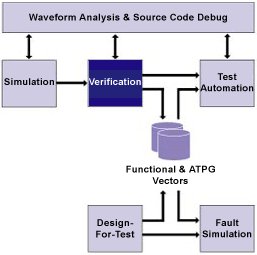

Super-FinSim是頂級的線性FinSim Verilog仿真器,從1993年放出第一款FinSim Verilog仿真器至今,FinSim Verilog已經引入了許多嶄新的功能:混合編譯和解釋型仿真,仿真工廠可以讓工程師管理數以百計的同步仿真、分離和增量編譯、高性能保存和重啟、直接集成C代碼,無須PLI。

Super-FinSim 仿真環境由一個附帶OVI的Virology編譯器,一個仿真構件和一個仿真內核組成。Verilog編譯器用於(1)檢查設計的句法和語意的正確性,(2)依據設計要求產生配置仿真內核所要求的代碼和數據。(3)選擇性的產生一個供其它應用程序處理的中間格式表達。仿真構件用於鏈接構成一個仿真器所需要的所有文件,例如,編譯器的輸出和仿真內核。主C鏈接器用於此目的。仿真內核是所有Veilog設計仿真公共代碼。一旦配置完成,仿真內核就成為一個定制的Verilog設計的仿真器。Super-FinSim的仿真器可以運行

Super-FinSim Verilog 編譯器有一個快速和強大的能進行廣泛錯誤檢查和恢復的分析器。此外,分析器能產生標明潛在設計錯誤的警告信息代碼,例如,交換一個越界的數組元素。

Super-FinSim Verilog 編譯器支持來自Verilog-XL的一些編譯器選項,包括控制庫搜索功能的選項。為便於引用命令文件同樣得到支持。必需事先指定希望的Super-FinSim 仿真器模式,不管是編譯,解釋或編譯、解釋的混合狀態。如果不指定,Super-FinSim將會試圖仿真編譯模式下的整個設計,如果發現了一個許可的編譯仿真器,否則,將在解釋模式仿真設計。所有的編譯信息儲存在登記文件‘finvc.log’。

Super-FinSim仿真器使用仿真內核的波形例程接口支持實時波形顯示。最近的Super-FinSim從數據I/O的工程捕捉系統(ECS)和Veribest’s Veriscope支持實時波形顯示。用ECS波形顯示構造仿真器,必須指定選項‘-ecs’。用Veriscope波形顯示構造仿真器,必須指定選項‘-veriscope’。

以上圖片文字介紹來自E維軟件資訊網

- 上一頁:《首席建築師V10.07》(CHIEF.ARCHITECT.V10.07)酷秀網絡漢化版[光盤鏡像]

- 下一頁:《建築信息建模》(Autodesk Architectural Desktop)v2007 4CD[Bin]

- [編程開發]《超現代造型設計軟件》(Think3 ThinkDesign Suite 2009.3.110.190 MultiLanguage)多國語言(含中文)[光盤鏡像],行業軟件、資源下載

- [行業軟件]《Strata三維設計》(Strata Design 3D CX v6.0.1)[光盤鏡像]

- [系統工具]《PDF轉換大師》(ABBYY.PDF.Transformer)v3.0.100.216[壓縮包]

- [行業軟件]《建築成本管理和計算》(Nemetschek Allplan BCM v2009 MULTiLANGUAGE)[光盤鏡像]

- [軟件綜合]ODL-MT6-全球最新外匯、黃金交易平台

- [操作系統]《VMware.GSX.Server.v3.2.1.19281》v3.2.1.19281

- [安全相關軟件]《隱私痕跡保護工具》(Koingo Software Data Guardian)v1.7.3/含注冊機/Windows版本[壓縮包]

- [系統工具]《3DMark06 正式版》2006 v102 Basic

- [應用軟件]《系統優化軟件》(Fresh UI V8.69)綠色注冊版[壓縮包]

- [應用軟件]《壓縮軟件》(RARLAB WinRAR)v4.10 Final (x86-x64)[壓縮包]

- [其他圖書]《布線器實用教程》高清文字版[PDF]

- [人文社科]《明朝的那些人兒·朱元璋》(MingChaoDeNaXieRenEr·ZhuYuanZhang)全27集/文化中國

- [電腦基礎]《歐特克Maya官方教程》(Autodesk Maya Techniques Modeling With Math)[Bin]

- [人文社科]《愛情有毒》掃描版[PDF]

- [其他圖書]《建築工程造價員培訓教材》高清掃描版[PDF]

- [英語學習資料]《NBC夜間新聞(2013-1季)》(NBC Nightly News)NBC美國新聞資源帖~2013年轉到此貼更新-更新到2013年3月31日ET[m4v]

- [其他圖書]《龍吟榜·華文廣告精粹》(LongYin Review)[第45期(Dec.2004)][第46期(Feb.2005)][PDF]

- [其他圖書]《藥房裡買得到的傳世名方》掃描版[PDF]

- [生活圖書]《過日子要有技術含量》掃描版【PDF】

- [硬盤游戲]《天使之谷》(AngelicVale)

- 《CAD/CAE/CAM一體化軟件》(Dassault Systemes Catia P2 v5R18 SP4)多語版 Win32/64[ISO],行業軟件、資源下載

- 《Master CAM-X版漢化包(中英文轉換包)》(Mastercam-X)V10

- 《CATIA V5R17 P3 中文版》(CATIA V5R17 P3)V5R17 P3[ISO],行業軟件、資源下載

- 《嵌入式電子開發 Xilinx EDK v8.1 DVD》(Xilinx EDK v8.1 DVD)[ISO]

- 《CATIA V5R21 幫助文檔》(CATIA V5R21 English Online Documentation)[光盤鏡像]

- 《實時測量與控制模塊》(LabVIEW Real Time)v8.0[ISO]

- 《電子設計套件》(Xilinx.ISE.Design.Suite)v13.3[光盤鏡像]

- 《IMSI Design CAD 3DMax 16.2 2D設計》(IMSI Design CAD 3DMax 16.2)英文[ISO],行業軟件、資源下載

- 員工積分制管理系統(保證win7 64位系統完美運行)

- 《三維機械設計系統》(SolidWorks)2012 SP0.0 Win32|64 Multilingual[光盤鏡像]

- 《計量經濟學分析預測軟件》(EViews Enterprise Edition)v7.2.DT230511.Update.Only[壓縮包]

- 《標記設計》(Eurosystems EuroCut)Pro.6.1.0.9[Bin]

免責聲明:本網站內容收集於互聯網,本站不承擔任何由於內容的合法性及健康性所引起的爭議和法律責任。如果侵犯了你的權益,請通知我們,我們會及時刪除相關內容,謝謝合作! 聯系信箱:[email protected]

Copyright © 電驢下載基地 All Rights Reserved