《 電子設計/IO智能核檢軟件》(HDL Works IO Checker)v2.2 R3[壓縮包] 簡介: 中文名 : 電子設計/IO智能核檢軟件 英文名 : HDL Works IO Checker 資源格式 : 壓縮包 版本 : v2.2 R3 發行時間 : 2012年 制作發行 : HDL Works 語言 : 英文 簡介 : 軟件類型:軟件>行業軟件 軟件性質:破解軟件 操作系統:Windows 應用平

電驢資源下載/磁力鏈接資源下載:

全選

"《 電子設計/IO智能核檢軟件》(HDL Works IO Checker)v2.2 R3[壓縮包]"介紹

中文名: 電子設計/IO智能核檢軟件

英文名: HDL Works IO Checker

資源格式: 壓縮包

版本: v2.2 R3

發行時間: 2012年

制作發行: HDL Works

語言: 英文

簡介:

軟件類型:軟件>行業軟件

軟件性質:破解軟件

操作系統:Windows

應用平台:Winall

問題反饋:http://www.hdlworks.com/support/index.html

網站鏈接:http://www.hdlworks.com/products/iochecker/index.html

軟件簡介 :

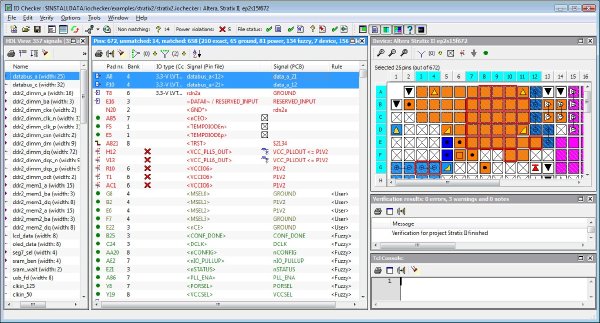

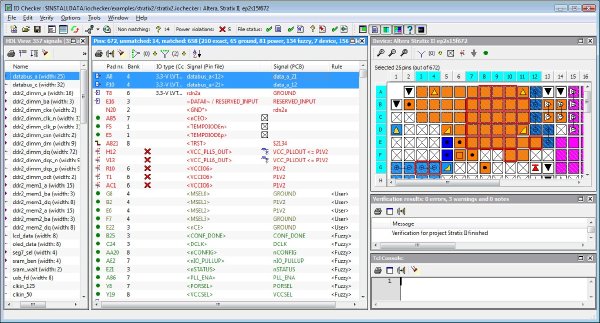

當使用大型FPGA上確保FPGA的引腳連接到正確的信號PCB的是一個繁重的任務。FPGA側的引腳分配形式在FPGA上實現的邏輯頂層的HDL信號。PCB上側引腳連接到正確的網,將連接在PCB上其他元件。由於FPGA和PCB的實施往往是並行完成,所使用的信號名稱並不總是相同。為了使事情更糟糕的,它往往是要執行針掉期,以防止PCB布線問題。這些引腳互換FPGA和PCB。由於這是幾乎總是體力勞動,和當前的設備已超過1500針,一個錯誤是很容易的。

Verifing一個FPGA在6分鐘內

驗證的FPGA

智能驗證在6分鐘內

IO檢查使用規則(基於正則表達式)在FPGA和PCB設計環境相匹配的信號名稱。它允許工具來驗證匹配的群體雖然單個信號仍然可以有所不同。這些規則可以自動生成由設計師微調。自動化的方法往往會匹配所有器件引腳的80%至90%。

檢查的IO的靈活性,允許它在任何設計流程中使用,不需要任何的設計方法。在與排序的問題的看法相結合的規則發生器,使工程師能夠驗證在半小時內1000 +引腳設備。

一旦該項目及其規則的定義,它是一個簡單的任務,以保持FPGA和PCB數據的一致性。所有過時的文件是在一個動作處理,並報告所有的改變都。

在6分鐘內創建的約束

創建約束

在6分鐘內

IO檢查概述

特點和優點

比較FPGA和PCB的引腳名使用正則表達式

創建和更新FPGA約束文件

自動規則生成363

電源引腳的電壓檢查

用戶指示接受驗證差異

單擊驗證和一致性

報告增量的變化,在引腳和淨列表

集中在十幾差異,而不是千行

適用於任何設計流程

HTML報告

資源更新列表

http://www.VeryCD.com/i/5190747/create/fol...postTime

When using large FPGA's on a PCB making sure that the FPGA pins are connected to the right signals is a cumbersome task. On the FPGA side the pins are assigned to the HDL signals that form the toplevel of the logic implemented on the FPGA. On the PCB side the pins have to be connected to the proper net that will connect it to other components on the PCB. Because implementation of FPGA and PCB is often done in parallel, the signal names used are not always identical. To make things even worse, it is often necessary to perform pin swaps to prevent PCB routing problems. These pin swaps have to be made both on the FPGA and the PCB. As this is almost always manual work, and current devices have over 1500 pins, a mistake is easily made.

Intelligent Verification

IO Checker uses rules (based on regular expressions) to match the signal names in both the FPGA and PCB design environment. It allows the tool to validate groups of matches although individual signals can still differ. The rules can be generated automatically and be fine-tuned by the designer. The automated approach will often match 80% to 90% of all device pins.

The flexibility of IO Checker allows it to be used in any design flow and does not require any design methodology. The rules generator in combination with the sorted problem view allows engineers to validate a 1000+ pins device in half an hour.

Once the project and its rules are defined it is a simple task to keep the FPGA and PCB data consistent. All out-of-date files are processed in one action and all changes are reported.

Features & Benefits

- Compare FPGA and PCB pin names using regular expressions

- Create & update FPGA constraint file

- Automatic rule generation

- Voltage checks for power pins

- User directed acceptance of verified differences

- One click verification and consistency

- Reports incremental changes in pin- and net list

- Concentrate on a dozen differences instead of a thousand lines

- Fits in any design flow

- HTML report

Home Page - http://www.hdlworks.com/products/iochecker/index.html

代碼

英文名: HDL Works IO Checker

資源格式: 壓縮包

版本: v2.2 R3

發行時間: 2012年

制作發行: HDL Works

語言: 英文

簡介:

軟件類型:軟件>行業軟件

軟件性質:破解軟件

操作系統:Windows

應用平台:Winall

問題反饋:http://www.hdlworks.com/support/index.html

網站鏈接:http://www.hdlworks.com/products/iochecker/index.html

軟件簡介 :

當使用大型FPGA上確保FPGA的引腳連接到正確的信號PCB的是一個繁重的任務。FPGA側的引腳分配形式在FPGA上實現的邏輯頂層的HDL信號。PCB上側引腳連接到正確的網,將連接在PCB上其他元件。由於FPGA和PCB的實施往往是並行完成,所使用的信號名稱並不總是相同。為了使事情更糟糕的,它往往是要執行針掉期,以防止PCB布線問題。這些引腳互換FPGA和PCB。由於這是幾乎總是體力勞動,和當前的設備已超過1500針,一個錯誤是很容易的。

Verifing一個FPGA在6分鐘內

驗證的FPGA

智能驗證在6分鐘內

IO檢查使用規則(基於正則表達式)在FPGA和PCB設計環境相匹配的信號名稱。它允許工具來驗證匹配的群體雖然單個信號仍然可以有所不同。這些規則可以自動生成由設計師微調。自動化的方法往往會匹配所有器件引腳的80%至90%。

檢查的IO的靈活性,允許它在任何設計流程中使用,不需要任何的設計方法。在與排序的問題的看法相結合的規則發生器,使工程師能夠驗證在半小時內1000 +引腳設備。

一旦該項目及其規則的定義,它是一個簡單的任務,以保持FPGA和PCB數據的一致性。所有過時的文件是在一個動作處理,並報告所有的改變都。

在6分鐘內創建的約束

創建約束

在6分鐘內

IO檢查概述

特點和優點

比較FPGA和PCB的引腳名使用正則表達式

創建和更新FPGA約束文件

自動規則生成363

電源引腳的電壓檢查

用戶指示接受驗證差異

單擊驗證和一致性

報告增量的變化,在引腳和淨列表

集中在十幾差異,而不是千行

適用於任何設計流程

HTML報告

資源更新列表

http://www.VeryCD.com/i/5190747/create/fol...postTime

When using large FPGA's on a PCB making sure that the FPGA pins are connected to the right signals is a cumbersome task. On the FPGA side the pins are assigned to the HDL signals that form the toplevel of the logic implemented on the FPGA. On the PCB side the pins have to be connected to the proper net that will connect it to other components on the PCB. Because implementation of FPGA and PCB is often done in parallel, the signal names used are not always identical. To make things even worse, it is often necessary to perform pin swaps to prevent PCB routing problems. These pin swaps have to be made both on the FPGA and the PCB. As this is almost always manual work, and current devices have over 1500 pins, a mistake is easily made.

Intelligent Verification

IO Checker uses rules (based on regular expressions) to match the signal names in both the FPGA and PCB design environment. It allows the tool to validate groups of matches although individual signals can still differ. The rules can be generated automatically and be fine-tuned by the designer. The automated approach will often match 80% to 90% of all device pins.

The flexibility of IO Checker allows it to be used in any design flow and does not require any design methodology. The rules generator in combination with the sorted problem view allows engineers to validate a 1000+ pins device in half an hour.

Once the project and its rules are defined it is a simple task to keep the FPGA and PCB data consistent. All out-of-date files are processed in one action and all changes are reported.

Features & Benefits

- Compare FPGA and PCB pin names using regular expressions

- Create & update FPGA constraint file

- Automatic rule generation

- Voltage checks for power pins

- User directed acceptance of verified differences

- One click verification and consistency

- Reports incremental changes in pin- and net list

- Concentrate on a dozen differences instead of a thousand lines

- Fits in any design flow

- HTML report

Home Page - http://www.hdlworks.com/products/iochecker/index.html

代碼

²

²²ÜÜÜÜ

Þ²ÛÛÛÝ

Þ²ÛÛÛÝ ß ÜÜÜÜÜÜÜÜÛÜÜ

ÞÛÛÛÛÝßßßßßßßßÛÛÜÜ ÜÜÜÛßßßßßßßÛÛÜÜ ÜÜ ² ÜÛßßßßßß ÜÜÜ ßÛÛßßßßßßßßßßßßÛÜÜ

ÞÛÛÛÛÛßßßÛÛÛÛÜÜÜ ßÛÛß ÜÜÜÛÛßßÛÜÜÜ ßßßÛÛß ²ÜÜÜÜÛÛßßßÛÛÛÛÛÝß ÜÛÛÛÜÛßßÛÛÛÜÜÜ ß

ÛÛÛÛÛÛ ßÛÛÛÛÛÜ ÜÛÛÛÛß ßÛÛÛÛÛÜ Ý ÜÛ²ÛÛÛß ÞÛÛÛÛÛ ÛÛÛÛÛß ßÛÛÛÛÛÛÜ

ÞÛÛÛÛÝ ÞÛÛÛÛÛ ÛÛÛÛÛÝ ÞÛÛÛÛÛÝ ÞÛ²²ÛÛ ÛÛÛÛÛÝÞÛÛÛÝ ÞÛÛÛÛÛÛÝ

ÞÛÛÛÛÝ ÛÛÛÛÝÞÛÛÛÛÛ ÜÛÛÛÛß Ûß²²ÛÝ ÞÛÛÛÛÝÞÛÛÛÝ ÛÛÛÛÛÛÛ

ÞÛÛÛÛÝ ÛÛÛÛ ÛÛÛÛÛÝ ÜÜÛßßß ÜÜÜÛ²ÛÝ ÞÛÛÛÛÝÞÛÛÛÝ ÛÛÛÛÛÛÛÝ

ÞÛÛÛÛÝ ÛÛÛÛÝÞ²ÛÛÛÛ ÜÜÛÛÛÛÛÛ²ÞÛ ÞÛÛÛÛÝÞÛÛÛÝ ÞÛÛÛÛÛÛÝ

ÞÛÛÛÛÝ °°°° ÞÛÛÛÛÛ²²ÛÛÛÛÝ °°°°° ÜÛÛÛÛÛÛÛÛÛ² ÛÝ °°°°° ÛÛÛÛÛÝÞÛÛÛÝ °°°°° ÞÛÛÛÛÛÛÛ

ÞÛÛÛÛÝ ÜÛÛÛÛÛÛ²²ÛÛÛÛÛÝ ÛÛÛÛÛÛÛÛÛÛÝÞÛÜ ÞÛÛÛÛÛÝÞÛÛÛÝ ÞÛÛÛÛÛÛÝ

ÞÛÛÛÛÝ ÜÛÛÛÛÛß Ü ²ßÛÛÛÛÛÜ ÞÛÛÛÛÛÛÛÛÛÛ ßÛÛÜÜܲßÛÛÛÛÛÝÞÛÛÛÝ ÛÛÛÛÛÛÛ

ßßßßßÛÜßßßß ÜÜÜÜÛÛÛÛÜ ßßßßßßÛÜÜÜÛÛÛÛßßßß ÜÜÜÜÜÜÜÜܲ ßßßßß ßßßßß ÜÜÜÜ ÞÛÛÛÛÛÛß

ßßßÛÜÜÜÜÛßßßßß ßßßßßßßßÛÜÜÜÜÜÜÜÜÜÜÛßßßßsQz²ßßßßßßßßßßßßßßßß Ûßßß

²ß

ß²

ÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜ

ÛÛÛßßß ßßßÛÛÛ

Ûß IO Checker v2.2 R3 (C) HDL Works ßÛ

Ûß ßÜ

² ÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄ ²

± Disks: 7 x 5,00mb Date : December 22, 2012 ±

° OS : Windows Type : Crack °

Ü ÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜ ÜÜ Ü

ßÜßß

Ûß

² Release Description:

± ~~~~~~~~~~~~~~~~~~~

Verifying hundreds of FPGA IO pins between PCB and FPGA in minutes

- When using large FPGA's on a PCB making sure that the FPGA pins are

connected to the right signals is a cumbersome task. On the FPGA side

the pins are assigned to the HDL signals that form the toplevel of the

logic implemented on the FPGA. On the PCB side the pins have to be

connected to the proper net that will connect it to other components

on the PCB. Because implementation of FPGA and PCB is often done in

parallel, the signal names used are not always identical. To make

things even worse, it is often necessary to perform pin swaps to

prevent PCB routing problems. These pin swaps have to be made both

on the FPGA and the PCB. As this is almost always manual work, and

current devices have over 1500 pins, a mistake is easily made.

Intelligent Verification

- IO Checker uses rules (based on regular expressions) to match the

signal names in both the FPGA and PCB design environment. It allows

the tool to validate groups of matches although individual signals can

still differ. The rules can be generated automatically and be fine-tuned

by the designer. The automated approach will often match 80% to 90% of

all device pins.

- The flexibility of IO Checker allows it to be used in any design flow

and does not require any design methodology. The rules generator in

combination with the sorted problem view allows engineers to validate

a 1000+ pins device in half an hour.

- Once the project and its rules are defined it is a simple task to keep

the FPGA and PCB data consistent. All out-of-date files are processed in

one action and all changes are reported.

°

Ü ÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜ ÜÜ Ü

ßÜßß

Ûß Installation:

² """""""""""""""

± Just unpack and install. Unrar crack.rar to installdir\bin\pc.

°

Ü ÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜ ÜÜ Ü

ßÜßß

Ûß Greetz:

² """""""""""""""

°

Ü ÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜÜ ÜÜ Ü

ßÜßß

Ûß Contact Us:

² """""""""""""""

±

°

ßßÛÜÜÜÜ Ü Ü ÜÜÜÜÛßß

ßßßßßßßßßßßßßßßßßßßßßßßßßßßßßßßßßßßßßßßßßßßßßßßßßßßßßßßßßßßßßßßßßßßßßßßßßßß

- 上一頁:《HDL圖形設計工具》(HDL Works HDL Desing Entry EASE )v7.4.R9[壓縮包]

- 下一頁:《智能化專業CAD設計軟件》(Bricsys BricsCad Platinium)v13.1.15.41783[壓縮包]

相關資源:

- [應用軟件]《盲打訓練軟件》(TypingMaster Pro)v7.0.1.794/含破解文件[壓縮包]

- [應用軟件]《PDF-XChange Pro 強大的多功能PDF閱讀器和編輯器 簡體中文綠色破解版 更新4.0.0190.0》(PDF-XChange Pro)4.0.0190.0[壓縮包]

- [應用軟件]《金山毒霸2005+06正式版升級破解+通行證》毒霸2005正式版+2006體驗版(限量發行),應用軟件、資源下載

- [多媒體類]《Steinberg Cubase 4》(Steinberg Cubase 4)4.1.3.853[安裝包]

- [應用軟件]《OpenOffice.org 2.0 for Linux》(OpenOffice.org 2.0 for Linux)正式版[ISO],應用軟件、資源下載

- [軟件綜合]【感謝天感謝地】祝明天也能有超強的rp++++為小組獻上multisim10和11

- [操作系統]微軟MSDN簡體中文&英文原版windows nt 4.0操作系統

- [應用軟件]《文件影像及管理方案》(LaserFiche)v7.2[Bin]

- [應用軟件]《PaloAlto 商業計劃書 15周年版/含注冊機》( Business Plan Pro 15th Anniversary Edition ) CAN v11.25.0009 含注冊機[壓縮包]

- [系統工具]《桌面下雪屏保1.0》簡體中文綠色版[壓縮包]

- [硬盤游戲]《方塊生物》(Cubis Creatures)v0.5.1硬盤版[壓縮包]

- [人文社科]《中國歷代器物圖冊》(高豐 & 程曉平)掃描版[PDF]

- [教育科技]《量子力學》(錢伯初)掃描版[PDF]

- [光盤游戲]《幻想三國志2+續緣篇》(Fantasia.Sanguo.2.Chinese.BIG5)繁體中文免CD破解版--更新補丁

- [人文社科]《幸福在於心態》掃描版[PDF]

- [生活圖書]《醫師神手絕技之秘傳點穴推拿醫療絕技》掃描

- [人文社科]《一個半世紀以來的上海猶太人—猶太民族史上的東方一頁》(潘光)掃描版[PDF]

- [生活百科]《內經講義》掃描版[PDF] 資料下載

- [教育綜合]德軍王牌:大德意志師(上中下)(周明 馬文俊 著

- [其他資源綜合]《美國紐約攝影學院攝影教材-上下冊》(NEW YORK INSTITUTE OF PHOTOGRAPHY)無密碼全目錄版 資料下載

- 《Ashlar 工業產品制圖》(Ashlar Vellum Graphite v8.4.6 SP1R4)[壓縮包]

- 《犀牛4.0(Rhino)渲染器及使用教程》(Flamingo2.0 & V

- 《靈圖領航者最新升級包》[壓縮包]

- 《建築三維渲染軟件》(Abvent.Artlantis.Studio)v3.0.2.1-REDT[壓縮包]

- 《Delphi可視化編程環境》(Rapid Application Development )xe3[壓縮包]

- 《歐特克三維機械設計軟件 》(AutoCAD Inventor Suite 2011 )2011[光盤鏡像]

- 《智能工程繪圖工具包》(CAD SCHROER STHENO ADVANCED V3.1.1)[光盤鏡像]

- 《建築三維渲染軟件》(Abvent Artlantis Studio)v4.1.7 Multilang[壓縮包]

- 《樂透彩劵軟件》(Data Solutions Lotto Pro 2011)v7.76[壓縮包]

- 《AutoTRAX EDA 數字模擬電路仿真軟件》(AutoTRAX EDA 9.72)最新版[安裝包]

- 《明星工廠照片MTV制作系統破解版面市!》(mtv)明星工廠照片MTV制作系統破解版面市!,行業軟件、資源下載

- 《邊界掃描工具軟件》(Ricreations Universal Scan)v9.4g[壓縮包]

免責聲明:本網站內容收集於互聯網,本站不承擔任何由於內容的合法性及健康性所引起的爭議和法律責任。如果侵犯了你的權益,請通知我們,我們會及時刪除相關內容,謝謝合作! 聯系信箱:[email protected]

Copyright © 電驢下載基地 All Rights Reserved