《電子設計自動化》(SynaptiCAD Product Suite v13.33a)[壓縮包],行業軟件、資源下載 簡介: 中文名: 電子設計自動化英文名: SynaptiCAD Product Suite v13.33a資源格式: 壓縮包發行時間: 2009年地區: 美國語言: 英文簡介: ynaptiCAD公司出品的EDA(電子設計自動化)工具集合,包括HDL輸入、仿真、測試、波形分析、管腳映射工具等等,是一個很完整的EDA方案。 包含了9種功能強大的工具:TestBencher Pro;BugHun

"《電子設計自動化》(SynaptiCAD Product Suite v13.33a)[壓縮包],行業軟件、資源下載"介紹

中文名: 電子設計自動化英文名: SynaptiCAD Product Suite v13.33a資源格式: 壓縮包發行時間: 2009年地區: 美國語言: 英文簡介:

ynaptiCAD公司出品的EDA(電子設計自動化)工具集合,包括HDL輸入、仿真、測試、波形分析、管腳映射工具等等,是一個很完整的EDA方案。

包含了9種功能強大的工具:TestBencher Pro;BugHunter Pro;VeriLogger Pro;WaveFormer Pro;SimuTAG;PinPort;DataSheet Pro;Timing Diagrammer Pro;Gigawave Viewer 。

1.TestBencher Pro:用於從獨立於語言的時序邏輯表生成交互式VHDL,Verilog, OpenVera,e, 和TestBuilder 測試基准及總線功能的模型。生成的測試基准能提供基於仿真相應的不同的激發向量,以便於測試基准功能作為一個被測試系統環境的動作模型正常工作。 TestBencher Pro是一個優秀的測試大規模FPGA 和 ASIC設計的工具。

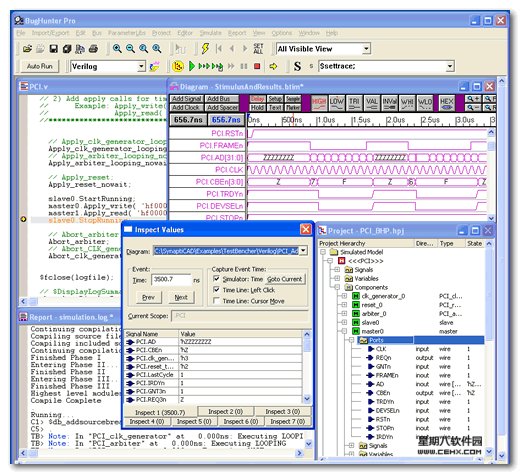

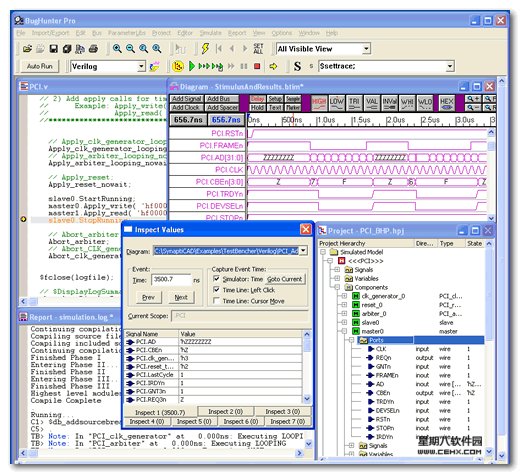

2.BugHunter Pro:一款用於 Verilog, VHDL 和 C++ 模擬器的圖形調試系統。BugHunter 支持所有主要的 HDL 模擬器,其主要功能包括:單一步驟調試、波形數據串流、項目管理等等。可以偵測程序與幫助系統的交互過程從而發現問題所在。

3.VeriLogger Pro:Verilog模擬器軟件。提供一個綜合了傳統Verilog模擬器所有特征的仿真環境,它具有強大的圖形測試矢量產生器。VeriLogger的快速模型測試使用戶可以對設計中的每個模型進行“自底向上”的測試。

4.WaveFormer Pro:由時序圖分析器、模擬器和測試向量生成器組合而成。它為設計人員提供了一個集成的環境,可以用來開發數字和模擬線路的時序圖。 WaveFormer Pro可以由Spice模擬器,Mathematica,或Matlab等工具輸入模擬數據。還可以利用WaveFormer Pro 內部擁有的波形函數直接生成模擬信號;或者將從總線上得到的數字信號變換成模擬信號。還可以將模擬信號波形逐段線性地變換成Spice模擬器的電壓信號源。

5.SimuTAG:一款功能強大和實時地查證出 FPGAs 的錯誤的系統。可經由比較FPGA 功能規則反證RTL樣式模擬規則,迅速發現邏輯和綜合錯誤。

6.PinPort:提供數字硬件與Verilog 或C++的虛擬接口環境。

7.DataSheet Pro:時間表文件夾管理工具。

8.Timing Diagrammer Pro:時間表設計工具。

9.Gigawave Viewer:波形觀測器。

ynaptiCAD公司出品的EDA(電子設計自動化)工具集合,包括HDL輸入、仿真、測試、波形分析、管腳映射工具等等,是一個很完整的EDA方案。

包含了9種功能強大的工具:TestBencher Pro;BugHunter Pro;VeriLogger Pro;WaveFormer Pro;SimuTAG;PinPort;DataSheet Pro;Timing Diagrammer Pro;Gigawave Viewer 。

1.TestBencher Pro:用於從獨立於語言的時序邏輯表生成交互式VHDL,Verilog, OpenVera,e, 和TestBuilder 測試基准及總線功能的模型。生成的測試基准能提供基於仿真相應的不同的激發向量,以便於測試基准功能作為一個被測試系統環境的動作模型正常工作。 TestBencher Pro是一個優秀的測試大規模FPGA 和 ASIC設計的工具。

2.BugHunter Pro:一款用於 Verilog, VHDL 和 C++ 模擬器的圖形調試系統。BugHunter 支持所有主要的 HDL 模擬器,其主要功能包括:單一步驟調試、波形數據串流、項目管理等等。可以偵測程序與幫助系統的交互過程從而發現問題所在。

3.VeriLogger Pro:Verilog模擬器軟件。提供一個綜合了傳統Verilog模擬器所有特征的仿真環境,它具有強大的圖形測試矢量產生器。VeriLogger的快速模型測試使用戶可以對設計中的每個模型進行“自底向上”的測試。

4.WaveFormer Pro:由時序圖分析器、模擬器和測試向量生成器組合而成。它為設計人員提供了一個集成的環境,可以用來開發數字和模擬線路的時序圖。 WaveFormer Pro可以由Spice模擬器,Mathematica,或Matlab等工具輸入模擬數據。還可以利用WaveFormer Pro 內部擁有的波形函數直接生成模擬信號;或者將從總線上得到的數字信號變換成模擬信號。還可以將模擬信號波形逐段線性地變換成Spice模擬器的電壓信號源。

5.SimuTAG:一款功能強大和實時地查證出 FPGAs 的錯誤的系統。可經由比較FPGA 功能規則反證RTL樣式模擬規則,迅速發現邏輯和綜合錯誤。

6.PinPort:提供數字硬件與Verilog 或C++的虛擬接口環境。

7.DataSheet Pro:時間表文件夾管理工具。

8.Timing Diagrammer Pro:時間表設計工具。

9.Gigawave Viewer:波形觀測器。

- 上一頁:《歐特克CAD著色工具》(Autodesk Impression 3.0.23698)[光盤鏡像],行業軟件、資源下載

- 下一頁:《頻譜分析》(Agilent 89600 Series Vector Signal Analyzer V10.01)[光盤鏡像],行業軟件、資源下載

相關資源:

- [應用軟件]《軟件密鑰備份和恢復工具》(Nuclear Coffee Recover Keys)v5.0.2.57/多國語言版/含補丁和注冊機[壓縮包]

- [應用軟件]《網絡分析工具》(Empirix Hammer Call Analyzer )v1.1.3[壓縮包]

- [編程開發]《天河軟件 》(PCCAD 2010 For AutoCAD 2010)2010[壓縮包],行業軟件、資源下載

- [軟件綜合]《專業處理PDF》(Foxit Phantom for veket)2.0[安裝包]

- [行業軟件]《圖形化編程語言》(NI LabVIEW)Professional v8.2[Bin]

- [應用軟件]《PDF制作轉換軟件》(Nuance PDF Converter Professional v5.0)更新企業版[Bin],應用軟件、資源下載

- [多媒體類]《3DS MAX V9.0 英文DVD光盤版》(Autodesk 3DS MAX V9.0)3DS MAX V9.0 英文完整光盤版[ISO]

- [行業軟件]《Altera (FPGA)電子設計軟件》(Altera Quartus II)V9.0 SP2[光盤鏡像]

- [應用軟件]《店鋪管理》(SHOPKEY5 SERVICE WRITER SHOP MANAGEMENT)V5.7[Bin]

- [操作系統]《蘋果雪豹操作系統正式版》(Apple MacOSX Snow Leopard)10.6[光盤鏡像]

- [光盤游戲]《滅罪紅顏3:萬年不遇》(Womens Murder Club: Twice in a Blue Moon)[光盤鏡像]

- [系統工具]《系統優化工具》(TuneUp Utilities 2012)更新v12.0.3000.140/含注冊機[壓縮包]

- [生活圖書]《中藥十八反研究》掃描版[PDF]

- [行業軟件]《SolidWorks Enterprise PDM 2012 SP0.0》(SolidWorks Enterprise PDM 2012 SP0.0)2012[光盤鏡像]

- [多媒體類]《音樂創作軟件》(Ableton Suite)v8.1.4[光盤鏡像]

- [人文社科]《不期而至 第二季》(Life Unexpected Season 2)全13集[720P]

- [人文社科]《鋼筆楷書規范字帖》掃描版[PDF]

- [網絡軟件]《軒轅劍4:黑龍舞兮雲飛揚》(XuanYuan Sword 4)v1.04b簡體中文硬盤版[安裝包] 免費下載

- [光盤游戲]《太空游俠2:統治者》(Space Rangers 2 :Dominators)RA Game

- [光盤游戲]《嘉年華大亨》(Ride Carnival Tycoon)[Bin]

- 《Delcam 模具設計》(Delcam PowerSHAPE v8.0)多國語言含中文[光盤鏡像],行業軟件、資源下載

- 《部件創建工具軟件》(AutoDesk Subassembly Composer for Civil3D)2011 2012 x86|x64[壓縮包]

- 《終極化學生物設計軟件》(CambridgeSoftware ChemBioOffice Ultra 2008 v11.01)[Bin]

- 個人工資計算器 1.0 綠色版

- 《科學實驗室》(scilab for veket)5.3.1中文版[壓縮包]

- 《AutoCAD2005 韓文版》(AutoCAD2005)[ISO],行業軟件、資源下載

- 《CAD設計制圖》(DICAD Strakon/S v2008 SP1 Multilanguage)[Bin]

- 《西門子工控》(Siemens SIMATIC Step7)v5.4[Bin],行業軟件、資源下載

- 《天正電氣8.2 下載版 包含注冊機及教程》天正電氣8.2[光盤鏡像]

- 《CimatronE.v8.0

- 《PowerMILL 8.0.01測試版 新增PowerMILL 8.0.02》(PowerMILL 8.0.01) 8.0.01,行業軟件、資源下載

- 《CimatronE.v8.0-SHooTERS 模具加工》[Bin]

免責聲明:本網站內容收集於互聯網,本站不承擔任何由於內容的合法性及健康性所引起的爭議和法律責任。如果侵犯了你的權益,請通知我們,我們會及時刪除相關內容,謝謝合作! 聯系信箱:[email protected]

Copyright © 電驢下載基地 All Rights Reserved